Schematic Integrity AI Analysis

What is schematic integrity AI analysis?

In today’s fast-paced world, it’s more important than ever to ensure that the engineering deliverables are correct at every stage of the research and development process, as well as that the verification processes are running smoothly and efficiently. One key aspect of this is ensuring that the schematic diagrams that are getting released for you by your team or by a third-party vendor are accurate and reliable. This is where schematic integrity AI analysis comes in.

Schematic integrity AI analysis is a service that uses artificial intelligence (AI) to analyze and verify the accuracy and completeness of your schematic designs. This can be especially useful for companies that have large and complex systems, as manual analysis of these systems can be time-consuming and prone to error.

Why is schematic integrity AI analysis extremely valuable?

The circuit design of a printed circuit board defines numerous qualities of an electronic device. Electrical and functional characteristics, reliability, longevity, manufacturability, price, etc. So far the market suggested no efficient instruments for automated schematic design validation. Schematic integrity AI analysis by Sintecs is the one.

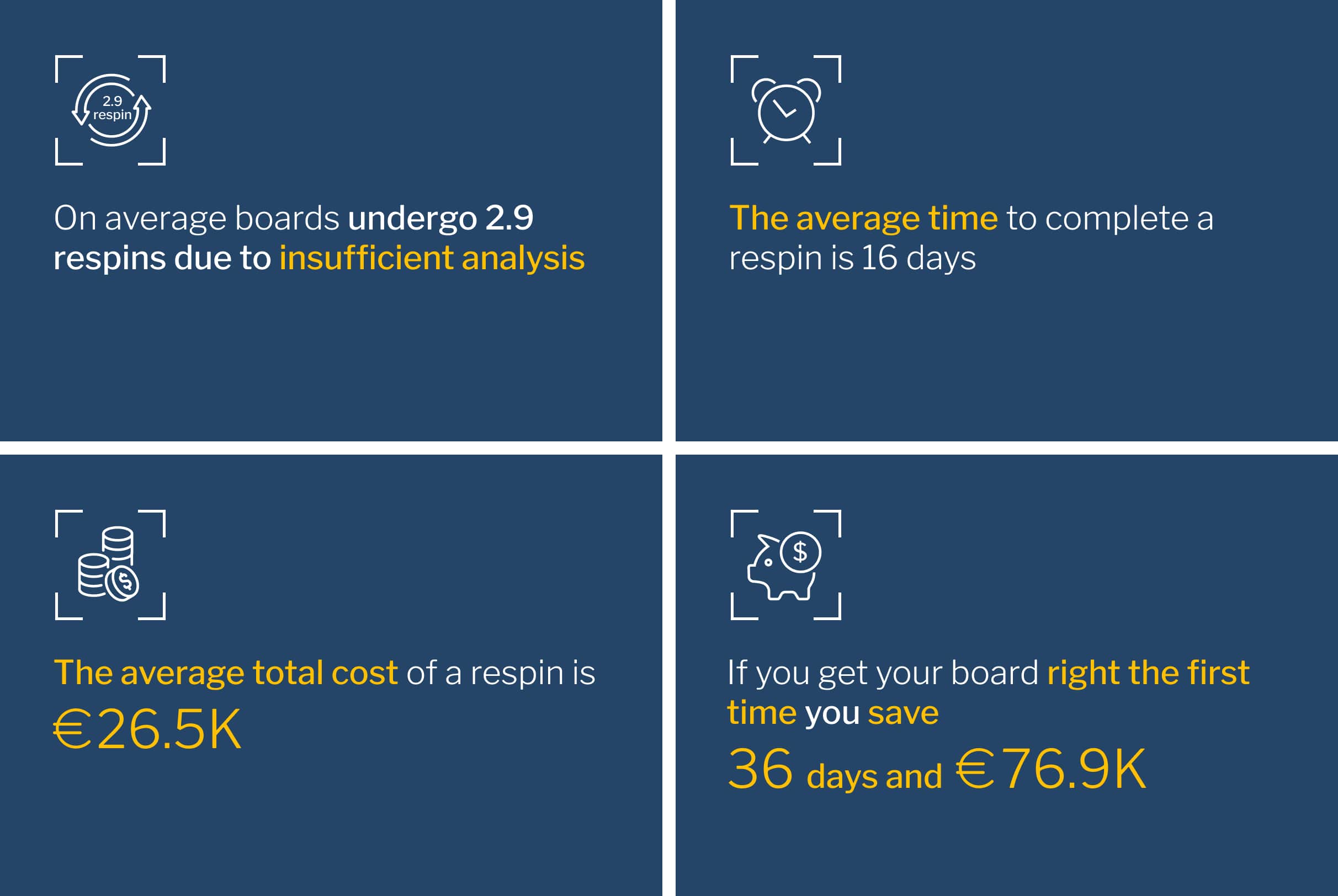

If a newly released schematic design is incorrect, it can potentially lead to various harmful business outcomes:

- The extra cost of new prototypes

- Additional time expenses on testing and debugging

- Additional working time expenses on applying corrections both in hardware design and PCB layout

- Re-running signal integrity analysis, DDR timing simulations, DFM verification, EMC tests, and other quality-related procedures

- General delay on the project conveyor will shift other projects causing commercial losses

- Additional time expenses on manufacturing and production support

- Direct market losses due to release delay, especially when competitor devices can be released at approximately the same time

- Company’s reputational losses

Sources: Lifecycle Insights, Research Gate

On the other hand, if your schematic diagrams are getting released with no errors with a higher automation level, it can lead to cost savings and improved productivity naturally. By using schematic integrity AI analysis, your engineering team can have a higher trust in the reliability of each developed design.

How schematic integrity AI analysis works

The process of schematic integrity AI analysis begins by inputting your latest schematic design and bill of materials (BOM) into the AI application. The AI engine then analyzes the schematic diagram, comparing it to a set of requirements and standards defined in the various specifications. If the AI finds any discrepancies or inconsistencies, it will flag them for further review by an engineer.

One of the key benefits of using AI for schematic integrity analysis is that it can analyze large amounts of data quickly and accurately. This means that schematic integrity AI analysis can catch errors and suggest necessary updates to your schematics in a timely manner.

From a technological point of view, schematic integrity AI analysis as an R&D stage is able to successfully replace both manual cross-verification between different hardware engineers and checklists checkups, saving days and weeks of valuable working time and bringing close product release date.

Input data

Netlist has to be presented in one of the following formats:

- Siemens EDA Xpedition and PADS Professional – export the netlist in QCV format

- OrCAD or Allegro – export “.dat” files (pstchip.dat, pstxprt.dat, pstxnet.dat)

- Altium Designer – export the netlist in Telesis or Protel2

- EAGLE – export “netlist” and “partlist” files

- KiCAD – export the default KiCAD netlist

The bill of materials (BOM) is also a mandatory part of the initial data. The preferred formats are “xlsx” or “csv” files with at least 2 separate columns inside 1. Manufacturer’s part number 2. Part’s reference designator

Related documentation

![]() Leaflet about schematic integrity AI analysis [PDF, 2 pages]

Leaflet about schematic integrity AI analysis [PDF, 2 pages]

![]() Presentation about schematic integrity AI analysis [PDF, 8 slides]

Presentation about schematic integrity AI analysis [PDF, 8 slides]

![]() Workshop over a real design [ZIP, 4 files]

Workshop over a real design [ZIP, 4 files]

Your next step

We offer freeware schematic integrity analysis run for all new customers. Are you ready to take the next step with schematic integrity AI analysis? Get in touch with us!