HyperLynx VX.2.12 Release Overview

Siemens EDA (ex-Mentor Graphics) released days ago a new version of the VX toolset under the index 2.12. The updated package includes, of course, a refreshed set of HyperLynx solutions for signal and power integrity. Sintecs, as an official specialized distributor of HyperLynx, is happy to make you familiar with the latest improvements already available for all the users of HyperLynx SI and PI bundles.

Short overview of the changes:

- DDRx Interface

- DDR5 Eye Diagram Results Prediction to Probability of 1e-16

- Additional DDR controller deskewing support

- Serial Link

- Generation of a SerDes compliance short report

- SerDes Compliance Analysis

- Improved 3D area modelling

- Power Distribution Network

- Improved sink pin modelling

- Other general improvements

- Reduced database load times

- Updated 3D board viewer

- IBIS Updates & General Automation

- Xcelerator share support

DDR5 Eye Diagram Results Prediction to Probability of 1e-16

The DDR5 specification requires 1e-16 probability level, which is not always possible for IBIS or IBIS-AMI models. HyperLynx Advanced DDRx AMI algorithm raises the accuracy of IBIS-AMI approach in terms of rise/fall asymmetry associated with DDR signals and suggests users simulation results down to the values 1e-16.

The complete list of the algorithm’s new and updated features:

- Accurately models rise/fall asymmetry

- Works with AMI models & Tx/Rx jitter specs

- Fast; runs simulations in seconds

- Works with crosstalk analysis

- Eyes plotted with probabilities in colour

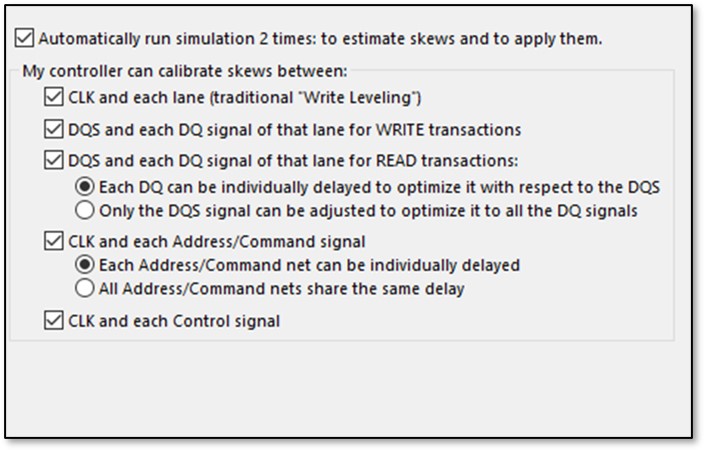

Address and Command Deskewing within DDR5 Simulations

HyperLynx is traditionally able to emulate various controller timing behaviours. VX.2.12 has now the new ability to model controllers to optimize timing Command / Address signals by class or at the individual bit levels.

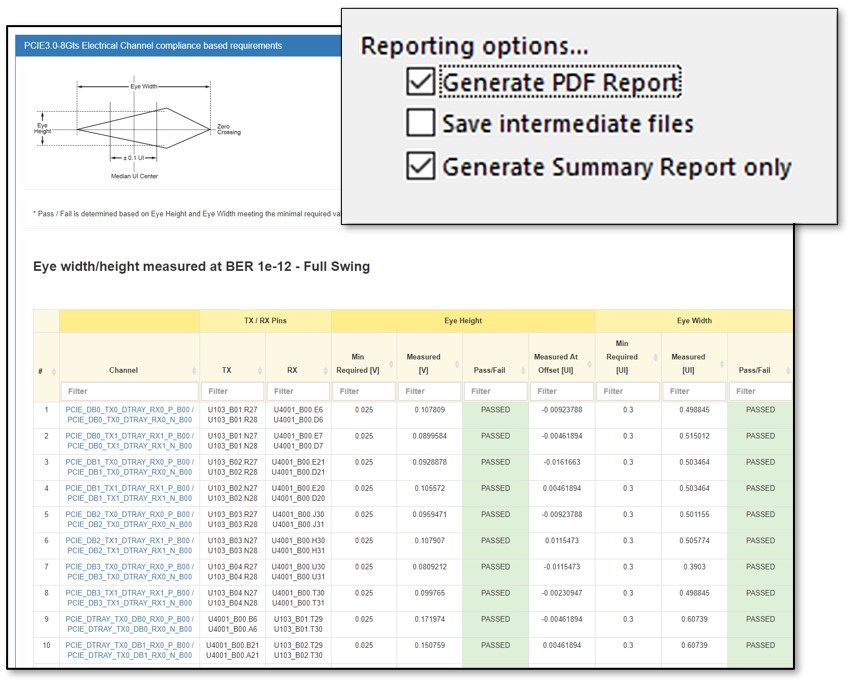

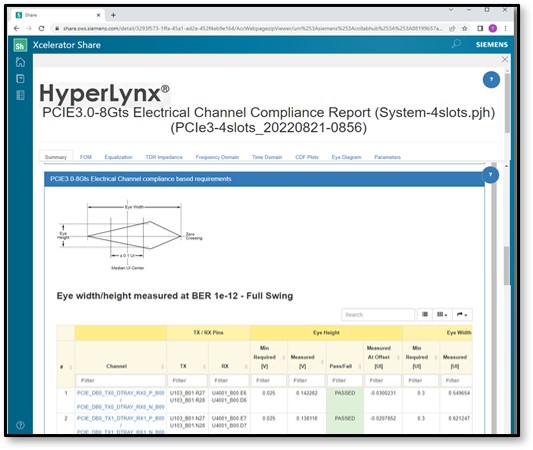

SerDer compliance short report

VX.2.12 provides now a shorter report with just the summary information helping to quickly find the signals which might need further attention.

- A shorter report is easier to read; lists pass/fail status and operating margin

- Helpful when screening many links to determine which links need a more detailed investigation

SerDes Compliance Analysis

SerDes compliance analysis in VX.2.12 includes new VEC/VEO Measurements required for 112Gb/s IEEE/OIF:

- Includes support for new FOM type

- Improves measurements when the eye is closed

- Reports weight function and vertical cross-section of the integrated eye diagram

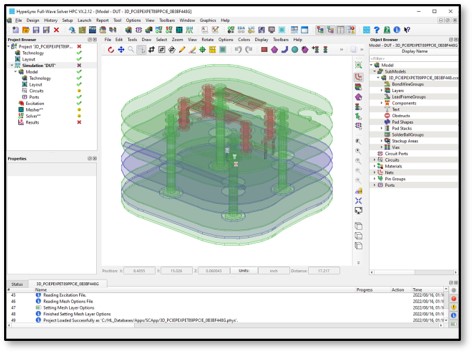

Improved 3D area modelling

Automated 3D area creation feature has been significantly improved in the VX.2.12 release. Now the generated areas get smaller and as a result solve faster. The names also became shorter through the use of a hashing algorithm that improves the reusability of 3D areas, meaning that fewer unique areas have to be solved.

- Smaller areas solve faster while producing equivalent results

- 3D area names are shorter and improve reuse through hash tags

Automated port de-embedding has also been improved making the whole automated process more reliable.

- Improvements to support smaller areas

- Improved performance

- Support for more complex geometries including curved traces

HyperLynx has now improved auto-port generation for complex connector geometries.

Sintecs is an authorized specialized distributor of HyperLynx having its own signal integrity and power integrity engineering teams. We are able to support customers at the highest level of expertise

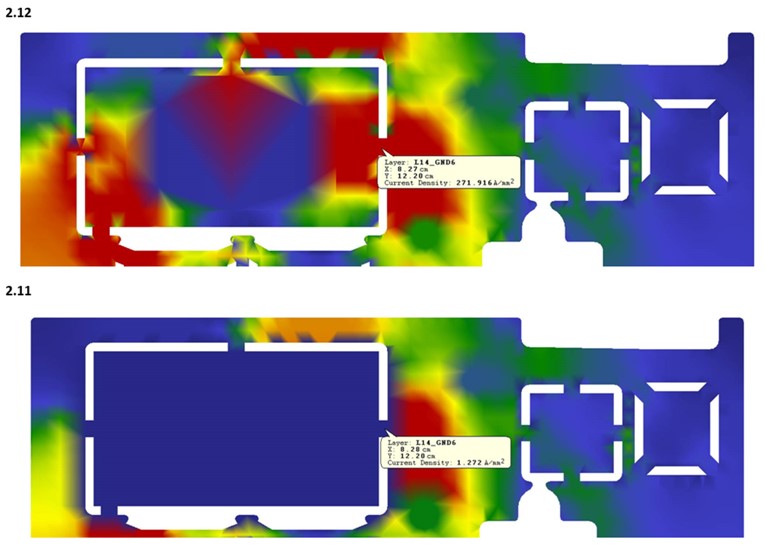

DC Drop: improved sink pin modelling

- HyperLynx VX.2.12 implements a new compromise where the current source occupies half the pin area. This excludes the cases of over-optimistic current distributions for source pins. As well as large current densities for single-point current sources.

- Current distributions are predicted more realistically.

Reduced database load times

HyperLynx VX.2.12 optimizes your design load time by creating an optimized data model, or .odm file which doubles load speed for large designs. .odm files are created for designs loaded from Siemens (.cce files) and Cadence layout tools.

.odm load time optimization works with HyperLynx SI/PI (BoardSim), HyperLynx Apps, HyperLynx DRC, HyperLynx Advanced Solvers.

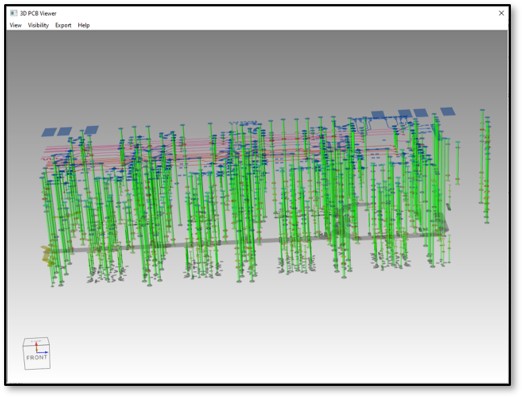

Updated 3D board viewer

The 3D viewer in BoardSim is now in line with the viewers of Xpedition and PADS Professional and uses the license features from those tools. The 3D viewer allows you to select either the entire board or a user-defined area, which allows you to visualize the spatial relationships between signals and traces. The display data can also be exported to a .pdf file.

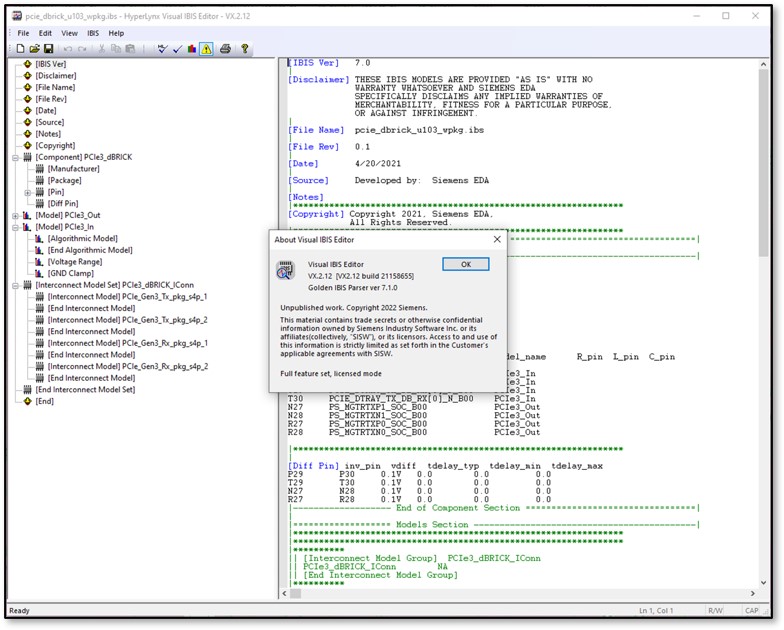

IBIS Updates & General Automation

HyperLynx SI has been updated to check IBIS simulation models in accordance with the 7.1.0 version of the IBIS specification. Automation updates improve the crosstalk thresholds management, and the ability to automatically check S-parameter files for causality and passivity in the Touchstone Viewer.

Xcelerator share support

Xcelerator Share allows HyperLynx SI/PI engineers to send simulation results to people with no access to HyperLynx through a cloud service. Users can assign tasks to each other, add comments and attach supporting files.

Sintecs is an authorized specialized distributor of HyperLynx having its own signal integrity and power integrity engineering teams able to support customers at the highest level of expertise. Contact Sintecs if you want to know more about the new release of HyperLynx, or about the existing offers we have. Additional information is also available on the website of Siemens EDA.