HyperLynx VX.2.13 SI and PI bundles updates

Siemens EDA (ex-Mentor Graphics) released days ago a new version of the VX toolset under the index VX.2.13. The new HyperLynx’s VX.2.13 update provides mainstream designers with cutting-edge simulation capabilities through the integration of advanced modeling and simulation methods with automated workflows that guide users through each step of the analysis.

Improvements in IBIS-AMI

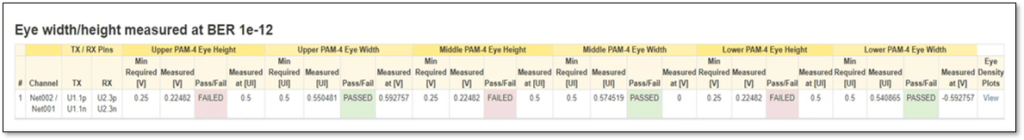

The automated measurements of IBIS-AMI models during PAM-4 simulations have been enhanced to provide upper, middle, and lower eye characteristics based on user-defined criteria. The latest simulator can automatically choose the time at which to measure eye height based on maximum eye height, use data from the IBIS-AMI model, or allow the user to set the time directly. Voltage thresholds for measurement can either be determined from the IBIS-AMI model or set by the user.

HyperLynx uses these selections to measure PAM-4 eyes automatically, reporting pass/fail results and degree of deviation.

DDR5 clock forwarding

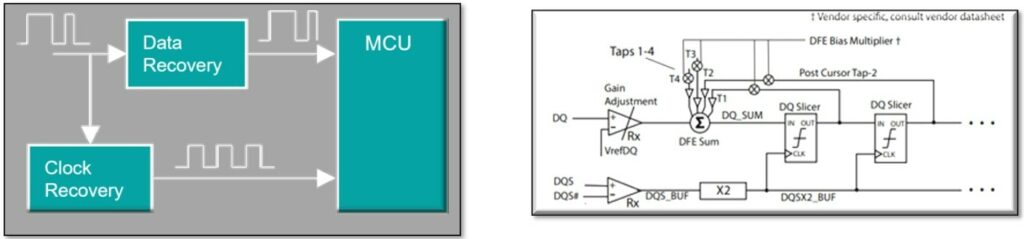

DDR5 memory introduces receive equalization to DRAM, which changes the way DDR memory is modeled and simulated. To model device-specific equalization and clocking behavior, IBIS-AMI models are used. Receiver clocking differs between serial links and DDR memory: SerDes receivers retrieve the sampling clock from the data stream, while DDR devices utilize a forwarded sampling clock (DQ strobe) signal that is transmitted with each byte lane to mitigate board-level noise.

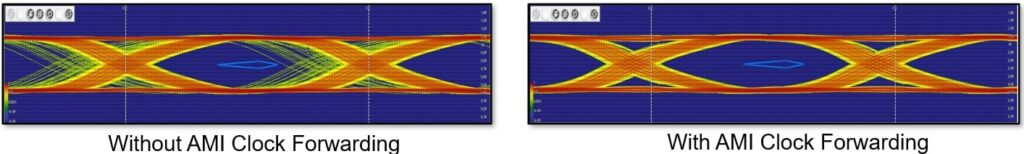

Accurate modeling of these effects necessitates a new type of IBIS-AMI model called a Clock-Forwarded AMI model. DDR5 models can now be clock-forwarded (more precise) or non-clock-forwarded (less precise).

Clock-forwarded models utilize a separate DQS input to generate the eye diagram, whereas non-clock-forwarded models assume the DQS is centered. HyperLynx is compatible with both models.

Compliance Reporting Improvements

HyperLynx SerDes Compliance Analysis offers an automated evaluation of serial channel designs to check for compliance with the relevant protocol standard. The compliance reports not only provide pass, fail, and margin data, but also detailed performance data of the channel, which can help identify channel problems without requiring re-simulation.

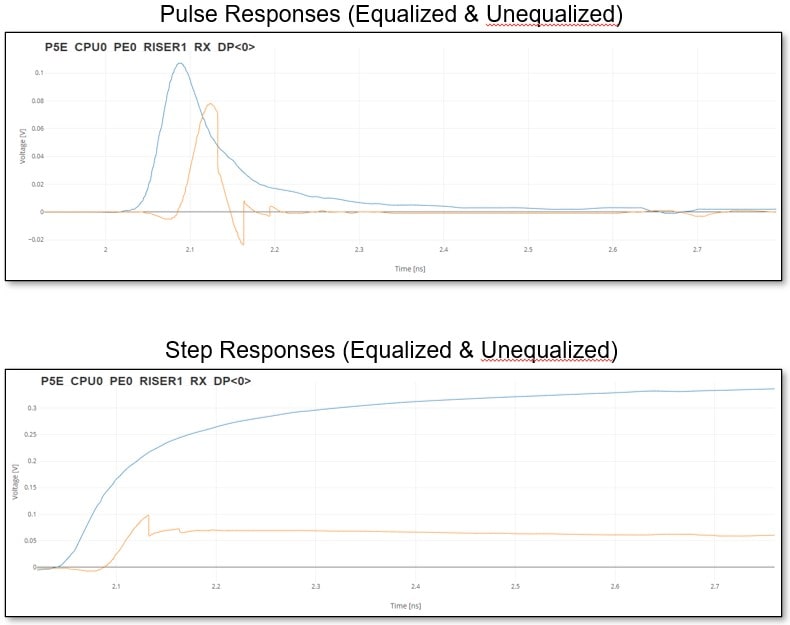

The interactive HTML report now features time-domain channel characterization data, enabling users to select, pan, and zoom waveform data for closer examination. The report includes unequalized pulse and step responses, which indicate the basic behavior of the channel, and equalized responses, which reveal the appearance of the data at the receiver after Tx and Rx equalization has done its best to enhance it.

Contact Sintecs using the contact forms or drop us a line via eda@sintecs.eu if you want to know more about the new release of HyperLynx, or about the existing offers we have. Sintecs is an official authorized distributor of Siemens EDA having its own signal integrity and power integrity engineering teams able to support customers at the highest level of expertise.