HyperLynx VX.2.11 Release

HyperLynx is a complete family of products for high-speed systems design and verification which consists of HyperLynx SI (Signal Integrity), HyperLynx PI (Power Integrity), HyperLynx Advanced Solvers, HyperLynx DRC (Design Rule Check) product lines.

The latest VX.2.11 release of HyperLynx delivers many improvements and additions to the existing products.

HyperLynx SI/PI

Serial Link Design & Verification

- SerDes analysis flow improvements

- New protocol support

- Table-based models

- Standards-based crosstalk models

DDRx Interface Design & Verification

- Improved DDR5 Support

- Power-Aware Improvements

HyperLynx DRC

- Distributed verification enhancements

- Improved support for vendor-specific rules

- New rules: Tiebarlocation, Component Net Topology

HyperLynx Advanced Solvers

- FWS performance / capacity improvements

- Job Distribution improvements

- New GUI

- Hybrid Solver support

HyperLynx Apps

- Pulse Response

- DC Drop

- Loop inductance

- SerDes Compliance

HyperLynx Design Space Explorer

- Automated, goal-driven design optimization

The new HyperLynx release supports 214 standard interface protocols and variants. Compared to VX.2.10, the newest HyperLynx SI release uses S-parameter models literally wherever it is possible, without replacing extra nets with their 2D counterparts.

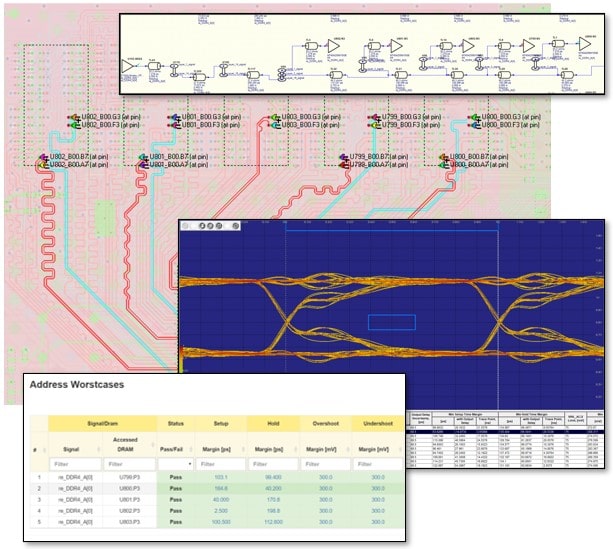

HyperLynx provides a complete, single-vendor solution for DDR4/5 interface design and verification that performs comprehensive signal integrity and timing analysis to validate all the signals in the interface and their relationships. It understands the requirements of all the different JEDEC specs and accommodates the device-specific requirements for different controllers. HyperLynx SI supports the same analysis flows and produces the same reports for both pre- and post-route analysis, so you can easily compare detailed pre-route expectations with actual post-route performance. It extracts post-route electromagnetic models for simulation automatically, so performing post-route analysis is simple – specify the nets you can about and thresholds for crosstalk, and HyperLynx does the rest. Power-aware simulation models simultaneous switching noise (SSN) and non-ideal return path effects, providing the accuracy needed to verify today’s highest speed and densest designs.

HyperLynx supports IBIS-AMI models for DDR5 simulation to the model controller and DRAM equalization. Traditional IBIS-AMI Statistical and Time-Domain simulation modes are supported, in addition to an Advanced DDRx AMI simulation mode, which provides additional accuracy by modelling nonlinear device behaviours associated with signal-ended signalling.

VX.2.11 adds support for the latest DDR5 IBIS-AMI features, including support for clock forwarded models. IBIS-AMI was originally developed for SerDes-based simulation, where the receiver clock is recovered from the received signal. Clock forwarding extends IBIS-AMI to accurately represent the way DDR5 devices actually work, where the received data strobe input is used to sample the incoming data bits.

HyperLynx provides complete, workflows for DDRx analysis that let you run simulations during PCB layout, to find and resolve problems earlier in the design cycle!

Contact Sintecs if you want to know more about the new release of HyperLynx. Additional information is also available on the website of Siemens EDA.